Strona 11 z 16

Re: Komputer 8-bitowy

: wt, 23 sierpnia 2022, 17:36

autor: jethrotull

Tomasz Gumny pisze: ↑wt, 23 sierpnia 2022, 10:31

Powinna gdzieś być, jeśli się nie zbiła przy przeprowadzkach. Poszukam. W weekend będę w Poznaniu, to mogę pożyczyć. Czym programujesz?

Programuję za pomocą TL866. Nie wiem czy w piątek sam będę w Poznaniu, ale chętnie Ci wyślę te EPROMy (i znaczek powrotny), jeślu by była taka możliwość.

Re: Komputer 8-bitowy

: wt, 23 sierpnia 2022, 17:46

autor: staszeks

Jeżeli z kolegą nie wyjdzie to, ja mogę pomóc na zasadzie, przysyłasz, wsadzam do kasownika, wyjmuje pakuję i wysyłam na Twój koszt.

Ponosisz tylko koszty przesyłki.

Re: Komputer 8-bitowy

: pn, 12 września 2022, 20:46

autor: jethrotull

Dziękuję, Staszek, Tomek już mi użyczył swojej lampy i udało mi się wykasować wszystkie moje EPROMy z okienkiem. Wielkie podziękowania dla Tomka. Te stare EPROMy są potrzebne do karty graficznej, która, jak pisałem wcześniej ma buga w softwarze powodującego zniekształcenie pierwszej linii znaków.

Udało mi się też dodać do komputera wsparcie dla klawiatury PS2. Klawiatura taka komunikuje się po prostu za pomocą transmisji szeregowej, z jednym bitem stopu i jednym bitem parzystości, i dostarcza własnego zegara. Od strony sprzętowej sprowadza się to więc do połączenia klawiatury z DARTem, jedynie trzeba odwrócić sygnał zegarowy, bo DART spodziewa się wyzwalania zboczem narastającym a zegar klawiatury jest aktywny na zboczu opadającym.

Dodałem także do płyty głównej standardowe gniazdo dysku IDE40, do którego zwykłą taśmą znaną z pecetów podłączyłem dysk Compact Flash, dzięki czemu nie jest już potrzebna zewnętrzna karta z dyskiem.

Re: Komputer 8-bitowy

: pn, 26 września 2022, 15:08

autor: jethrotull

Oto zdjęcie dysku CF podłączonego do płyty głównej standardową "szmatą":

Obecnie buduję drugi egzemplarz komputera, mający tylko 32KB ROMu i 32KB RAMu i wspierający jedynie klawiaturę PS2. Docelowo będzie miał kartę graficzną VGA, podczas gdy pierwszy egzemplarz otrzyma kartę PAL.

Re: Komputer 8-bitowy

: wt, 27 września 2022, 18:40

autor: jethrotull

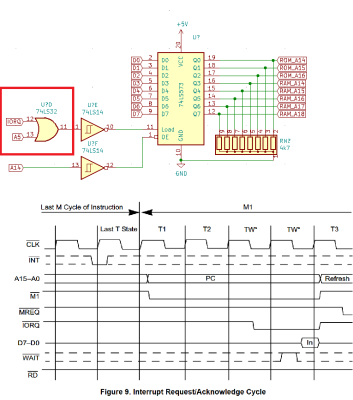

Wydaje mi się, że popełniłem potworny błąd projektując dekodowanie adresów urządzeń We/Wy. Dla przykładu pokażę schemat dekodowania przełączania banków pamięci, które, jak pamiętamy, jest aktywowane liniami A5 i IORQ. Obie te linie muszą być w stanie niskim jednocześnie, co dzieje się podczas wykonywania instrukcji OUT jeśli adres portu wynosi 11011111b:

To czego nie wziąłem pod uwagę, to że warunek ten może zająć także podczas cyklu potwierdzenia przerwania (interrupt acknowledge). W procesorze Z80 nie ma wolnych nóżek aby jedną poświęcić wyłącznie na potwierdzanie przerwania, konstruktorzy procesora użyli więc do tego celu pinu M1 i IORQ, które w innym przypadku nie są nigdy aktywne jednocześnie. W czasie potwierdzenia przerwania linia IORQ jest aktywna, na szynie adresowej pojawia się wartość licznika programu (czyli w zasadzie, z punktu widzenia urządzeń We/Wy, wartość losowa), a na szynie danych wektor przerwania. W moim komputerze jedyne urządzenie używające przerwań to klawiatura, a wektor tego przerwania to 00h. Oznacza to, że obsługa przerwania klawiatury może "niechcący" zapisać wartość 00h do rejestru banków pamięci. Póki co w czasie testów komputera nie zauważyłem żeby tak się działo, ale wydaje mi się jedyny tego powód to że adres procedury odczytu z klawiatury akurat zawiera ustawiony bit A5.

Podobny problem jest ze sterowaniem buzzerem. Tutaj problem jest również niezauważalny, a to zapewne dlatego, że naciśnięcie klawisza powoduje "kliknięcie" buzzerem (szybkie włączenie i wyłączenie) co maskuje jakąkolwiek przypadkową wartość wpisaną do przerzutnika sterującego buzzerem.

Jeszcze gorzej jest w przypadku cyklu potwierdzania przerwania niemaskowalnego, bo tam równieć linia RD procesora staje się aktywna. Trochę nie rozumiem czemu to nie powoduje żadnych obserwowalnych problemów, mimo że się dzieje 50 razy na sekundę.

Nie mam niestety za bardzo miejsca na płytce aby dodać jeszcze jeden czip który by dekodował linię M1, ale mam jeden zapasowy inwerter, wymyśliłem więc taki oto trick:

Re: Komputer 8-bitowy

: wt, 27 września 2022, 20:37

autor: Marek7HBV

Nie ma się tym za bardzo przejmować-w okienkach są tysiące

takich powiązań i najwyżej wystąpi ,,nieczekiwany wyjątek,,

.

Re: Komputer 8-bitowy

: wt, 27 września 2022, 20:43

autor: Tomasz Gumny

W czasie potwierdzenia przerwania linia IORQ jest aktywna, na szynie adresowej pojawia się wartość licznika programu (czyli w zasadzie, z punktu widzenia urządzeń We/Wy, wartość losowa),

Czy naprawdę nie dałoby się sprawić, żeby na szynie danych pojawiał się "nieszkodliwy" adres?

Re: Komputer 8-bitowy

: czw, 29 września 2022, 14:15

autor: jethrotull

Raczej nie. Dokumentacja procesora nie specyfikuje czy to co się pojawia na szynie adresowej to licznik programu w momencie wystąpienia przerwania czy w momencie obsługi przerwania. W tym drugim przypadku można by było jakąś sztuczką programową sprawić żeby ten adres miał wszystkie bity dekodujące urządzenia We/Wy ustawione (czyli nieaktywne), ale logicznie mi się wydaje, że musi to być adres gdzie procesor się znajduje w momencie otrzymania przerwania - przecież wtedy procesor jeszcze nie zna adresu procedury obsługi przerwania, po to potwierdza przerwanie żeby otrzymać wektor obsługi.

Mój plan w tym momencie to obsłuchać komputer sondą żeby się dowiedzieć czemu działa choć nie powinien i na pewno się podzielę wnioskami.

Re: Komputer 8-bitowy

: czw, 29 września 2022, 18:05

autor: Tomasz Gumny

Zdaje się, że klawiaturę odpytujesz w przerwaniu niemaskowalnym. W cyklu przyjęcia tego przerwania nie widzę aktywnego IORQ. Jest za to nieszkodliwa kombinacja MREQ i RD.

Re: Komputer 8-bitowy

: czw, 29 września 2022, 21:08

autor: jethrotull

Zgoda, przerwanie niemaskowalne nie będzie problemem, ale klawiaturę odczytuję przerwaniem maskowalnym.

Przerwanie maskowalne jest używane jako przerwanie synchronizacji pionowej.

Re: Komputer 8-bitowy

: pn, 3 października 2022, 19:50

autor: jethrotull

Mój pomysł za bardzo nie działa, wygląda na to że zbocze opadające na M1 (na anodzie diody) chwilowo ściąga wejście bramki OR do stanu niskiego (ale nie za każdym razem?), mimo że IORQ jest cał czas wysokie. Pewnie to jakaś bezwładność diody?

acknowledge.png

Re: Komputer 8-bitowy

: pn, 3 października 2022, 21:49

autor: Tomasz Gumny

Zapewne pojemność diody w połączeniu z pociągnięciem że "słabego" stanu wysokiego na IORQ w dodatku przez rezystor. Jaki dałeś rezystor, diodę i ile trwa szpilka?

Może lepszym rozwiązaniem byłaby logika na tranzystorach?

Re: Komputer 8-bitowy

: wt, 4 października 2022, 09:26

autor: jethrotull

Szerokość impulsu podana przez Logica to 0.125us, ale to po prostu szerokość jednej próbki, przy częstotliwości próbkowania 8MHz. Rezystor ma 1k, czyli pojemność diody wystarczy że by była zbliżona do 1pF.

Zaznaczam, że pozostałe układy We/Wy (oprócz przełączania banków), czyli klawiatura, buzzer, dysk i UART działają poprawnie, gdyż one dekodują też linie RD/WR. Problem dotyczy jedynie przełączania banków.

Chyba po prostu wepchnę gdzieś jeszcze na płytkę jeden układ scalony, albo w ogóle zrezygnuję z przełączania banków, którego w ogóle nie chciałem mieć i dostałem "przypadkiem", lub raczej w wyniku szeregu błędnych decyzji.

Re: Komputer 8-bitowy

: wt, 4 października 2022, 10:32

autor: jethrotull

Zapomniałem napisać: dioda Schottky.

Re: Komputer 8-bitowy

: wt, 4 października 2022, 20:36

autor: staszeks

Plącze się u mnie po półkach kilka książek o mikroprocesorach.

Być może je masz albo sąa dostępne w sieci.

jeżeli nie a uważasz, że jest tam coś przydatnego to kilka stron mógłbym w wolnych chwilach odskanować.

1. Modułowe systemy mikrokomputerowe

praca zbiorowa WN-T 1984